### **ECE 3401 Lecture 21**

# **Instruction Set Architecture**

### **Overview**

- Computer architecture

- Operand addressing

- Addressing architecture

- Addressing modes

- Elementary instructions

- Data transfer instructions

- Data manipulation instructions

- Floating point computationsProgram control instructions

- Program interrupt and exceptions

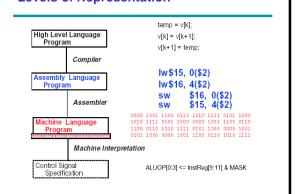

# Levels of Representation

### **Computer Architecture**

- Instruction set architecture

- A set of hardware-implemented instructions, the symbolic name and the binary code format of each instruction

- Organization

- Structures such as datapath, control units, memories, and the busses that interconnect them

- Hardware

- The logic, the electronic technology employed, the various physical design aspects of the computer

### **Example ISAs (Instruction Set Architectures)**

- RISC (Reduced Instruction Set Computer)

- Digital Alpha

- Sun Sparc

- MIPS RX000

- IBM PowerPC

- HP PA/RISC

- CISC (Complex Instruction Set Computer)

- Intel x86

- Motorola 68000

- DEC VAX

- VLIW (Very Large Instruction Word)

- Intel Itanium

### **Instruction Set Architecture**

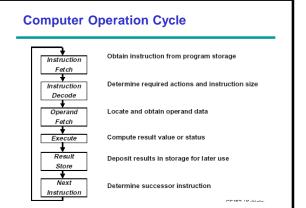

- A processor is specified completely by its instruction set architecture (ISA)

- Each ISA will have a variety of instructions and instruction formats, which will be interpreted by the processor's control unit and executed in the processor's datapath

- An instruction represents the smallest indivisible unit of computation. It is a string of bits grouped into different numbers and size of substrings (fields)

- Operation code (opcode): the operation to be performed

- Address field: where we can find the operands needed for that operation

- Mode field: how to derive the data's effective address from the information given in the address field

- Other fields: constant immediate operand or shift

### **Register Set**

- Programmer accessible registers (R<sub>0</sub> to R<sub>7</sub> in previous multi-cycle computer)

- Other registers

- Registers in the register file accessible only to microprograms (R<sub>8</sub> to R<sub>15</sub>)

- Instruction registers (IR)

- Program counter (PC)

- Pipeline registers

- Processor status register (PSR: CVNZ state)

- Stack pointer (SP)

### **Overview**

- Computer architecture

- Operand addressing

- Addressing architecture

- Addressing modes

- Elementary instructions

- Data transfer instructions

- Data manipulation instructions

- Floating point computations

- Program control instructions

- Program interrupt and exceptions

### **Operand Addressing**

- Operand: register value, memory content, or immediate

- Explicit address: address field in the instruction

- Implied address: the location of operand is specified by the opcode or other operand address

### **Three Address Instructions**

- Example: X=(A+B)(C+D)

- Operands are in memory address symbolized by the letters A,B,C,D, result stored memory address of X

- +: Short program, 3 instructions

- -: Binary coded instruction require more bits to specify three addresses

### **Two Address Instructions**

The first operand address also serves as the implied address for the result

5 instructions

#### **One Address Instructions**

Implied address: a register called an accumulator ACC for one operand and the result, single-accumulator architecture

```

LD

\mathsf{ACC} \gets \mathsf{M}[\mathsf{A}]

ADD

В

ACC \leftarrow ACC + M[B]

ST

M[X] \leftarrow ACC

Х

ACC \leftarrow M[C]

LD

С

7 instructions

\mathsf{ACC} \leftarrow \mathsf{ACC} + \mathsf{M[D]}

ADD

D

ACC ← ACC X M[X]

MUX

Х

M[X] \leftarrow ACC

ST

```

All operations are between the ACC register and a memory operand

#### **Zero Address Instructions**

```

Use stack (FILO):

```

```

TOS ← TOS + TOS.1

ADD

PUSH X

\mathsf{TOS} \leftarrow \mathsf{M}[\mathsf{X}]

• POP X

M[X] \leftarrow TOS

PUSH A

TOS ← M[A]

PUSH B

TOS \leftarrow M[B]

ADD

TOS ← TOS + TOS.1

PUSH C

\mathsf{TOS} \leftarrow \mathsf{M[C]}

8 instructions

PUSH D

TOS←M[D]

ADD

TOS ← TOS + TOS.1

TOS ← TOS X TOS.1

MUX

M[X] \leftarrow TOS

POP

```

- Data manipulation operations: between the stack elements

- Transfer operations: between the stack and the memory

#### Memory Address 100 Push: SP ← SP-1; TOS ← R1 SP=101 101 С Pop: В 102 • R1 ← TOS; SP ← SP +1

R1

Α

103

104

# **Addressing Architecture**

- Defines:

- Restriction on the number of memory addresses in instructions

- Number of operands

- Two kinds of addressing architecture:

- Memory-to-memory architecture

Only one register PC

- All operands from memory, and results to memory

- Many memory accesses

- Register-to-register (load/store) architecture

- Restrict only one memory address to load/store types, all other operations are between registers

registers  $R1 \leftarrow M[A]$   $R2 \leftarrow M[B]$   $R3 \leftarrow R1 + R2$   $R1 \leftarrow M[C]$   $R2 \leftarrow M[D]$   $R1 \leftarrow R1 + R2$   $R1 \leftarrow R1 \times R3$   $M[X] \leftarrow R1$ LD R1, A LD R2, B ADD R3,R1, R2 LD R1, C LD R2, D ADD R1.R1. R2 MUL R1, R1, R3 ST X, R1  $M[X] \leftarrow R1$

### **Addressing Modes**

**Stack Instructions**

- Address field: contains the information needed to determine the location of the operands and the result of an operation

- Addressing mode: specifies how to interpret the information within this address field, how to compute the actual or effective address of the data needed.

- Availability of a variety of addressing modes lets programmers write more efficient code

### **Addressing Modes**

- Implied mode implied in the opcode, such as stack, accumulator

- Immediate mode (operand) a = 0x0801234

- Register mode a=R[b]

- Register-indirect mode a =M[R[b]]

- Direct addressing mode a = M[0x0013df8]

- Indirect Addressing mode a= M[M[0x0013df8]]

- PC-relative addressing branch etc. (offset + PC)

- Indexed addressing a=b[1]

| Example               |                     |                   | ADRS or NBR=500 |                |            | R1=400           |  |

|-----------------------|---------------------|-------------------|-----------------|----------------|------------|------------------|--|

| Addressing mode       | Symbolic conversion | Register transfer | address o       | ontent<br>fACC | 250<br>251 | Opcode Mod       |  |

| Immediate             | LDA#NBR             | ACC←NBR           | -               | 500            | 252        | Next instruction |  |

| Register              | LDAR1               | ACC€R1            | -               | 400            | 400        | 700              |  |

| Register-<br>indirect | LDA (R1)            | ACC€M[R1]         | 400             | 700            | 500        | 800              |  |

| Direct                | LDAADRS             | ACC←M[ADRS]       | 500             | 800            |            |                  |  |

| Indirect              | LDA [ADRS]          | ACC←M[M[ADRS]]    | 800             | 300            | 750        | 600              |  |

| Relative              | LDA \$ADRS          | ACC←M[ADRS+PC]    | 750             | 600            | 800        | 300              |  |

| Index                 | LDA<br>ADRS(R1)     | ACC←M[ADRS+R1]    | 900             | 200            | 900        | 200              |  |

### **Overview**

- Computer architecture

- Operand addressing

- Addressing architecture

- Addressing modes

- Elementary instructions

- Data transfer instructions

- Data manipulation instructions

- Floating point computations

- Program control instructions

- Program interrupt and exceptions

| Instru              | Instruction Set Architecture                                                                                |                                                                   |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

|                     | RISC (reduced instruction set computers)                                                                    | CISC (complex instruction set computers)                          |  |  |  |  |

| Memory<br>access    | restricted to load/store<br>instructions, and data<br>manipulation instructions are<br>register-to-register | is directly available to most types of instructions               |  |  |  |  |

| Addressing mode     | limited in number                                                                                           | substantial in number                                             |  |  |  |  |

| Instruction formats | all of the same length                                                                                      | of different lengths                                              |  |  |  |  |

| Instructions        | perform elementary operations                                                                               | perform both elementary and complex operations                    |  |  |  |  |

| Control unit        | Hardwired, high throughput and fast execution                                                               | Microprogrammed, facilitate compact programs and conserve memory, |  |  |  |  |

### **Data Transfer Instructions**

- Data transfer: memory ←→ registers, processor registers ←→ input/output registers, among the processor registers

- Data transfer instructions

| Name     | Mnemoni |

|----------|---------|

| Load     | LD      |

| Store    | ST      |

| Move     | MOVE    |

| Exchange | XCH     |

| Push     | PUSH    |

| Pop      | POP     |

| Input    | IN      |

| Output   | OUT     |

|          |         |

### 1/0

- Input and output (I/O) instructions transfer data between processor registers and I/O devices

- Ports

- Independent I/O system: address range assigned to memory and I/O ports are independent from each other

- Memory-mapped I/O system: assign a subrange of the memory addresses for addressing I/O ports

# **Data Manipulation Instructions**

| Arithmetic           |              | Logical and bit manipulation |              | Shift instructions         |              |  |

|----------------------|--------------|------------------------------|--------------|----------------------------|--------------|--|

| Name                 | Mnemo<br>nic | Name                         | Mnem<br>onic | Name                       | Mnem<br>onic |  |

| Increment            | INC          | Clear                        | CLR          | Logical shift right        | SHR          |  |

| Decrement            | DEC          | Set                          | SET          | Logical shift left         | SHL          |  |

| Add                  | ADD          | Complement                   | NOT          | Arithmetic shift right     | SHRA         |  |

| Subtract             | SUB          | AND                          | AND          | Arithmetic shift left      | SHRL         |  |

| Multiply             | MUL          | OR                           | OR           | Rotate right               | ROR          |  |

| Divide               | DIV          | Exclusive-OR                 | XOR          | Rotate left                | ROL          |  |

| Add with carry       | ADDC         | Clear carry                  | CLRC         | Rotate right with<br>carry | RORC         |  |

| Subtract with borrow | SUBB         | Set Carry                    | SETC         | Rotate left with<br>carry  | ROLC         |  |

| Subtract reverse     | SUBR         | Complement carry             | COMC         |                            |              |  |

| Negate               | NEG          |                              |              |                            |              |  |

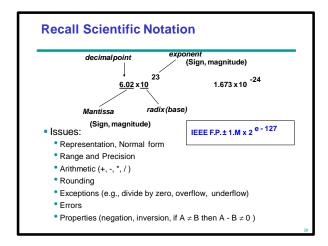

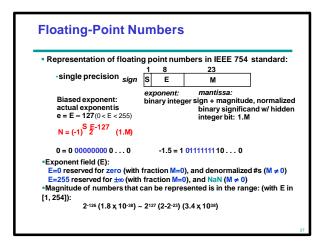

#### **Floating-Point Computation** • What can be represented in N bits? Unsigned 2<sup>N</sup>-1 to -2<sup>N-1</sup> to 2s Complement 2N-1 - 1 1s Complement -2<sup>N-1</sup>+1 to 2<sup>N-1</sup>-1 BCD 0 10<sup>N/4</sup> - 1 But, what about? • very large numbers? 9,349,398,989,787,762,244,859,087,678 • very small number? 0.000000000000000000000045691 rationals 2/3 •irrationals $\sqrt{2}$ transcendentals е